Alder Lake was not only the first to introduce to desktops an x86 hybrid architecture; the processors have also been pegged to leverage the high-velocity PCIe 5.0 interface. An open-source replacement for UEFI, Coreboot (via Komachi-Ensaka) appears to provide valuable information on the potential PCIe configuration that we could see on Alder Lake.

Early rumours suggested that both the PCIe 5.0 and PCIe 4.0 specifications will be supported by the 12th Generation Alder Lake processors, and Tim Wawrzynczak’s review of the code seems to confirm that. However, the code specifically references Alder Lake-P (ADL-P), so it is unclear whether the same setup would translate to the Alder Lake-S lineup.

We don’t know what Alder Lake-P is going to be yet, but some believe it could be Intel’s Atom P-series or a smartphone chip. In any case, a previous coreboot patch showed that Alder Lake-P could max out at 14 cores, six Golden Cove cores, and eight Gracemont cores.

Alder Lake-P appears to provide a flexible PCIe layout. One PCIe 5.0 x8 lane or two PCIe 4.0 x4 lanes are reportedly offered by the processor. It would seem that no interface allows bifurcation, which means that the PCIe 5.0 lane can not be split or get the PCIe 4.0 lanes to operate at x8. Nonetheless, for previous-gen models, both are backwards compatible.

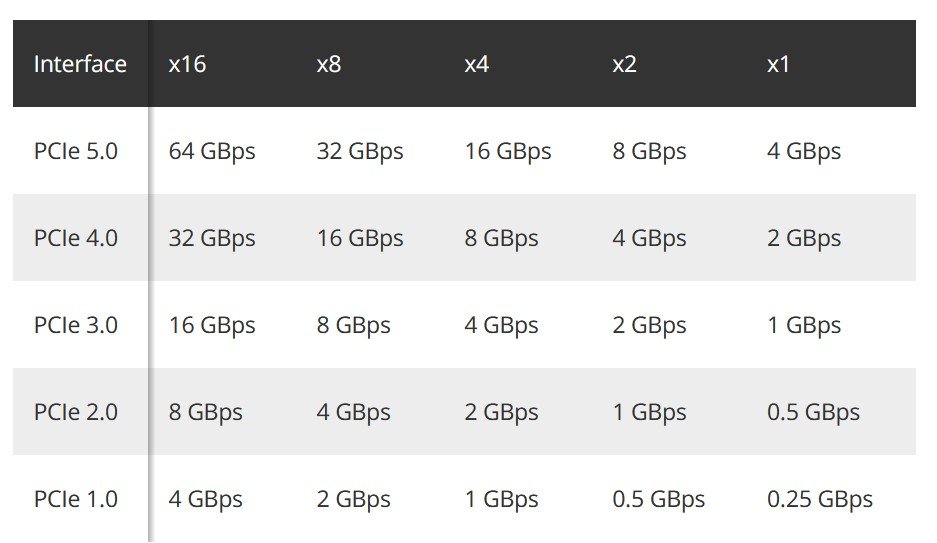

At first, a single PCIe 5.0 x8 lane might sound mediocre, but it offers plenty of bandwidth. PCIe 5.0 x8 is practically similar to PCIe 4.0 x16; therefore, the interface is good for up to 32 Gbps of bandwidth, which is greater than any PCIe-based consumer device can consume.

At this point, only AMD’s Ryzen 3000 and Ryzen 5000 mainstream processors have implemented the PCIe 4.0 standard. Intel’s imminent Rocket Lake should change that panorama.

Right now, there are quite a few mainstream PCIe 4.0 products on the market, including graphics cards and M.2 SSDs. Tests have shown that a PCIe 3.0 x16 interface still has to saturate even the fastest graphics cards, far less PCIe 4.0.